New publications updated!

Congrats to our members!

All articles are available on IEEEXplore.

2020 IEEE International Symp. on Circuits and Systems (ISCAS)

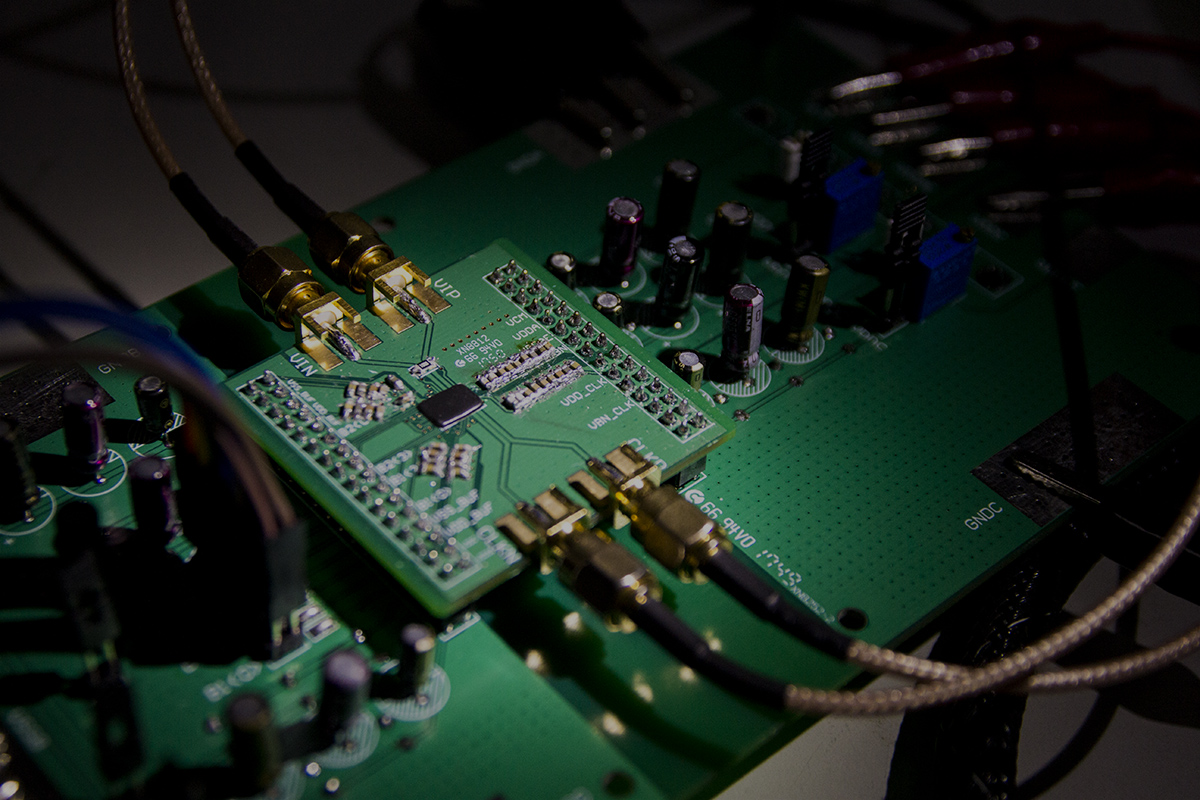

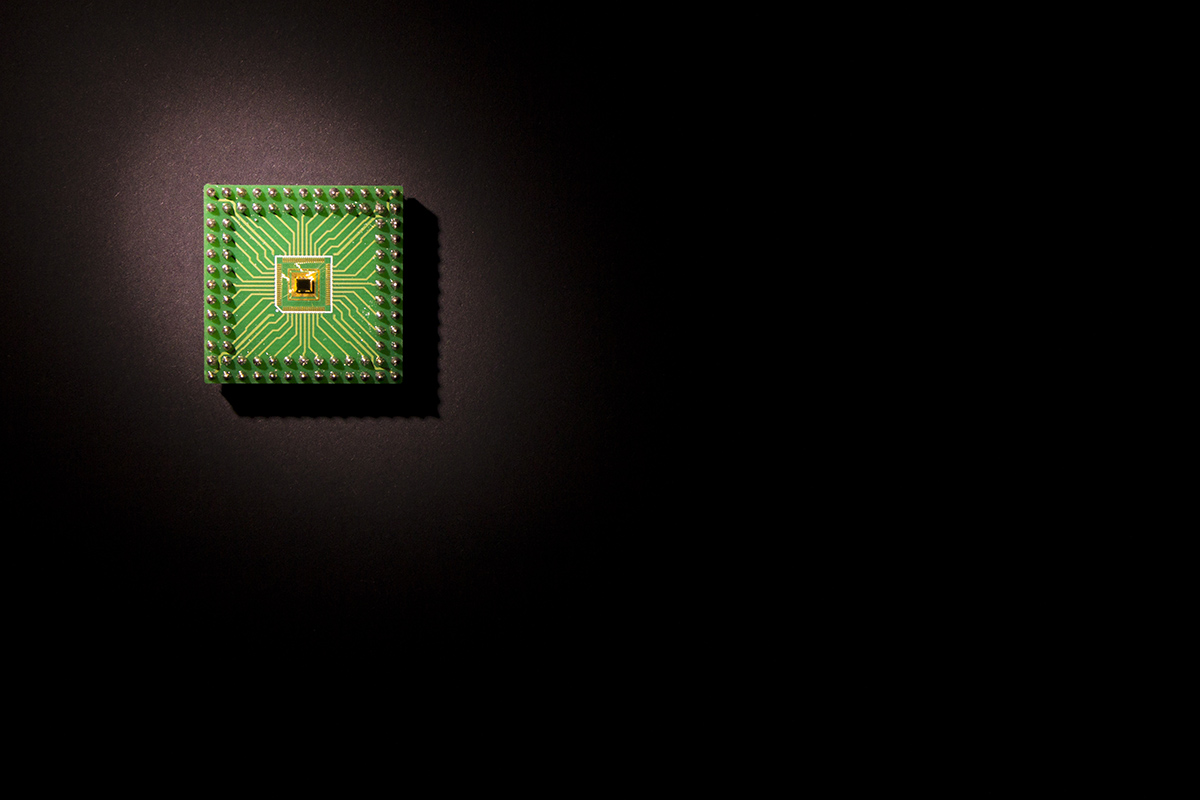

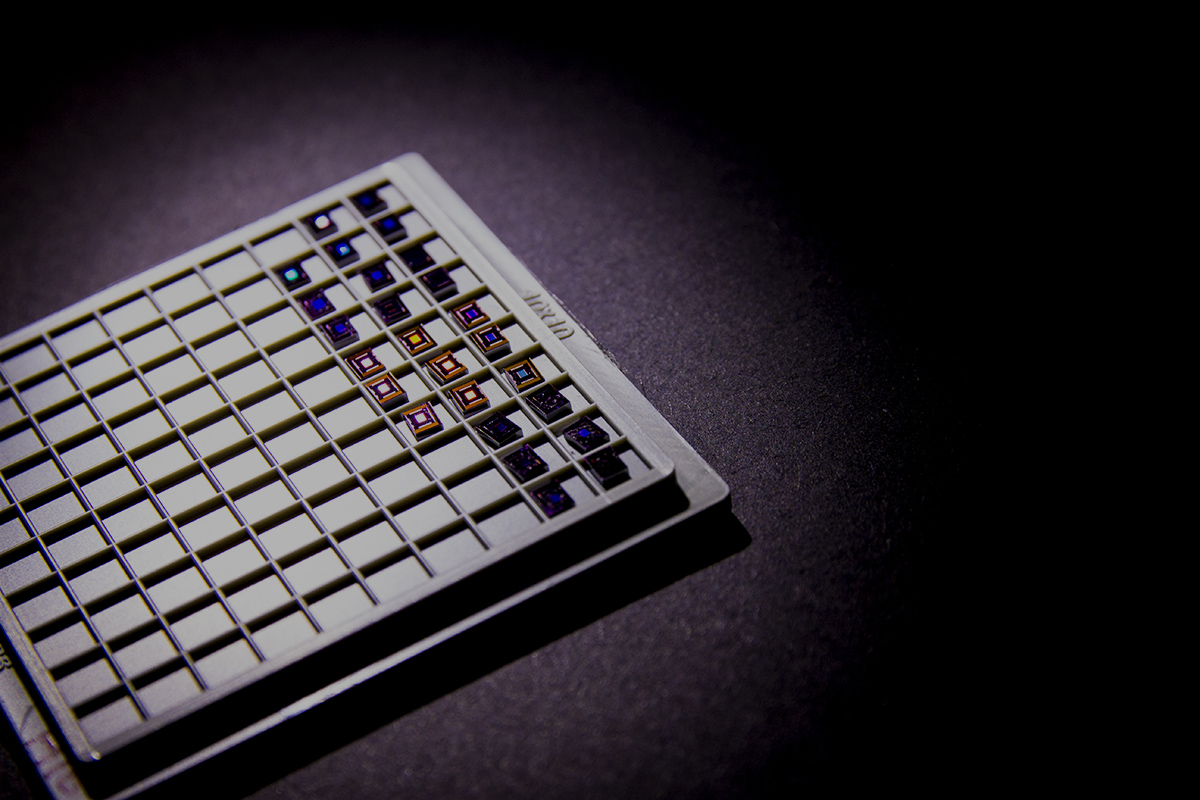

[1] You-Shin Chen, Tzu-Hsiang Hsu, Guan-Cheng Chen, Chien-Wen Chen, Chih-Cheng Hsieh, “A Monolithic Optical Encoder Using CMOS Image Sensor with Background Light Cancellation,” to be presented in 2020 IEEE International Symp. on Circuits and Systems (ISCAS), Oct. 2020.

閱讀全文